# 高速スイッチング対応の 小型SiCパワーモジュール

Compact SiC Power Module for High Speed Switching

豊島 茂憲\*

Shigenori Toyoshima

初川聡

平方 宣行 Noriyuki Hirakata

Satoshi Hatsukawa

築野 孝 Takashi Tsuno 御神村 泰樹

Yasuki Mikamura

SiCモジュールはSiモジュールと比較して高速スイッチングが可能であり、高周波化、低損失化が期待されている。しかし、高速化に伴いターンオフ時に過電圧が発生し、定格電圧を超えパワーモジュール及び回路の破壊につながる恐れが生じる。高速動作時の過電圧を抑制するためには、パワーモジュール内部の寄生インダクタンスの低減が必須である。我々は3次元電磁場シミュレータによる低インダクタンスモジュールの設計及び試作による検証を行った。この結果、ターンオフ時間20nsの高速スイッチングに対応したパワーモジュールを開発したので報告する。

A SiC power module can offer higher speed switching performance than a Si power module. Large voltage overshooting caused by fast turn off switching may damage the power module or application circuit itself by exceeding its absolute maximum ratings, where voltage overshooting must be proportional to the current changing rate and stray inductance in the module. In order to avoid such large overshooting, inductance reduction is needed. To overcome the problem, we carried out optimization of the inductance with a commercially available 3-dimensional electro-magnetic field simulator, and we assembled low resistance SiC MOSFET in the module. As a result, we have successfully developed a module suitable for high-speed switching in 20 ns.

キーワード:SiC パワーモジュール、MOSFET、SBD、内部インダクタンス、高速スイッチング

# 1. 緒 言

近年、温暖化防止、エネルギー資源の枯渇などの観点から、 省エネルギー化への必要性が高まっている。多くの場合、 エネルギーは電気エネルギーに変換された後に伝送され、 消費先で目的に応じて様々なエネルギーに再変換される。 このエネルギー変換に電力制御用半導体デバイス(以下、パ ワーデバイス) が近年、使用されて初めて、きめ細かい制御 が可能になり省エネルギーに大きく貢献してきた。更なる 省エネルギー化のためパワーデバイスの高性能化が求めら れている。これまで、パワーデバイスにはシリコン(以下、 Si) が広く使用されており、高耐圧用途では絶縁ゲートバイ ポーラトランジスタ (Insulated Gate Bipolar Transistor 以下、IGBT) が用いられる。特にインバータ等の大電流を必 要とする応用製品に対しては、複数の素子を組み合わせて 一体化させたパワーモジュールといわれる形態で使用され る。一方でSi IGBTは技術の成熟により物性値から決まる限 界性能に到達しようとしており、物性的にパワーデバイス に適しているワイドバンドギャップ半導体の炭化ケイ素 (以 下、SiC)を用いた金属酸化物半導体電界効果トランジスタ (Metal-Oxide-Semiconductor Field-Effect Transistor 以 下、MOSFET) に注目が集まっており、これまで当社でも開 発を行ってきた(1)、(2)。SiC MOSFETはSi IGBTに対し高耐圧 化、低オン抵抗化、高速スイッチングが可能である。パワー デバイスの損失は導通損失とスイッチング損失に分けられ、

SiCに期待される数10kHzから100kHzを超える動作ではスイッチング損失の占める割合が大きくなり、スイッチング損失はスイッチング時間に比例するため高速スイッチングがより一層求められている。

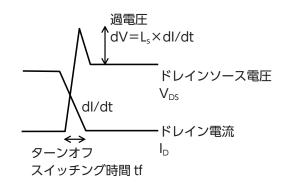

しかし、Si IGBTモジュールに実装される素子のみをSiC-MOSFETに置き換えただけでは、SiCの優れた性能を十分に生かすことができない。高速スイッチングにおける問題点としては、寄生インダクタンスL。による過電圧が知られている。高速スイッチングではdl/dtが大きくなり、図1のようにdV=-Ls・dl/dtで表される過電圧が発生する。既存パワー

図1 インダクタンスによる過電圧

モジュールのL。では過大電圧が発生し、素子の破壊を引き起こす危険が生じる。このため、SiC MOSFETの高速性をモジュールの利点としてアピールするためには、L。を低減したパワーモジュールの開発が必須である。

# 2. モジュールインダクタンス評価

まず、シミュレータにおけるインダクタンス計算の妥当性 を確認するため、既存のパワーモジュールに対してインダク タンスの実測値とシミュレーション値の比較を行った。

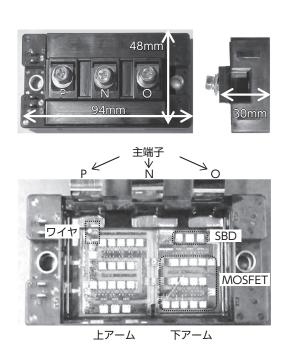

図2は市場に広く流通しているSiモジュールと端子配置、端子サイズなどの外形を同一にして、互換可能に設計した定格1200V 100Aのモジュール (以下、標準モジュール) である。この標準モジュールはMOSFET とショットキー障壁ダイオード (Schottky Barrier Diode 以下、SBD) の並列接続の組が2直列になる構造をとっている。

図2 標準モジュールとその内部構造 (Si-IGBT互換モジュール)

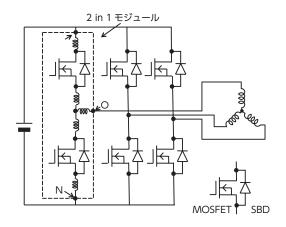

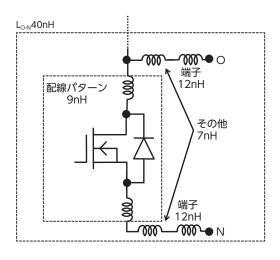

図3は3相インバータの回路図であり、点線の枠で囲まれた部分が標準モジュール1台分に該当する。MOSFETとSBDの並列接続の組が1つのパワーモジュールに2組直列に入っている場合、2 in 1モジュールと呼ばれ3相インバータの1相分を担う。正極側の組を上アーム、負極側の組を下アームと呼び、またそれぞれの主端子を図3のようにP、N、O端子と呼ぶ。

このパワーモジュールのインダクタンスを実測、シミュレーションの両面から確認した。JEC-2407-2007<sup>(3)</sup>に準

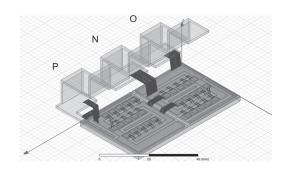

拠する測定方法で求めた所、O端子とN端子間のインダクタンスLonの実測値は40nHであった。次に、ANSYS Q3D Extractor™を使用し、シミュレーションを行った。**図4**のモデルを用いて、シミュレーションを行った結果Lon=40nHと実測と一致することを確認した。我々が開発した高効率SiC MOSFET (4)、(5) の搭載を想定した場合、ターンオフ時間20nsの高速スイッチングが可能であり、dl/dt=50kA/μs

図3 3相インバータ回路図

図4 計算モデル

図5 標準モジュール各部のインダクタンス

となる。よって、過電圧dVは200Vにも達すると推定される。各部位毎のシミュレーションにより求めたインダクタンスを図5に示す。端子部が各12nH、基板パターン及びワイヤが9nHであり、残りの7nHは主に主端子と配線パターン間のワイヤによるものと推測される。一般に、インダクタンスは配線長が長く細いほど大きくなる。標準モジュールは主端子が長く、且つ配線パターンの電流経路が細くなっているため、40nHと大きいインダクタンスを持っていると考えられる。

# 3. 低インダクタンスモジュール設計

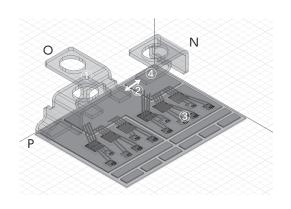

我々が開発した高効率SiC MOSFETを搭載することを想定し、定格1200V 100Aの2 in 1モジュールを設計した。過電圧dVは定格1200Vの10%以下にする必要がある。ターンオフ時間20ns, dl/dt=50kA/μsを想定し、我々は過電圧dVを100V以下とすべくL。<20nHとなるように設計した。標準モジュールは端子部のみで24nHと、20nHを超えてしまう。L。<20Hを満足するには外装から見直した新型のパワーモジュールの開発が必要となる。インダクタンスL。を減らすため下記の4点を考慮しパワーモジュールを設計した。

- ①自己インダクタンスを小さくするため、各主端子の電流 経路を最短にした。

- ②配線パターンの電流経路を短縮するためP端子とO端子、O端子とN端子を近づけ、且つ配線パターンを小型化させた。

- ③相互インダクタンスを利用し、低インダクタンス化を図るため、ソースワイヤをドレイン電流経路と平行にした。

- ④標準モジュールのように主端子をワイヤで配線パターン に接続するのではなく、半田接合にて直立させた。

図6中に上記4点を考慮して設計したモジュール内部構造を示す。また表1にシミュレーションの結果を示す。①、②と③、④のそれぞれの効果として各主端子、配線パターン、上記以外のインダクタンスがそれぞれ低減された。高速スイッチングに必要な条件、20nH以下を満たす結果が得られた。

図6 低インダクタンスモジュール計算モデル

表1 インダクタンス計算結果(単位:nH)

|        | 低インダクタンス<br>モジュール | 標準<br>モジュール | 差  |

|--------|-------------------|-------------|----|

| P, N端子 | 5                 | 12          | 7  |

| 〇端子    | 2                 | 12          | 7  |

| 配線パターン | 5                 | 9           | 4  |

| 上記以外   | 0                 | 7           | 7  |

| 合計     | 12                | 40          | 28 |

### 4. 試作、評価

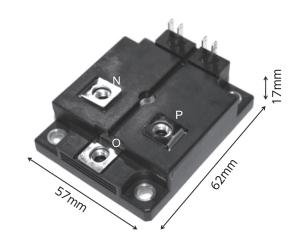

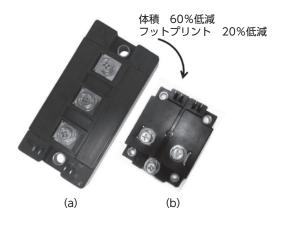

図7はシミュレーションを元に試作した低インダクタンスモジュールの外観図である。また、図8は標準モジュールとの比較である。低インダクタンス化を行い、電流経路を短くしたことに関連し、体積が60%、フットプリントが20%低減した。試作した低インダクタンスモジュールのインダクタンスの実測値は14nHであり、目標の20nHを下回る値が得られた。シミュレーション結果12nHとの差2nHは、シミュ

図7 低インダクタンスモジュール

図8 (a) 標準モジュール、(b) 低インダクタンスモジュール

レーションで簡略化したワイヤ等の細部の形状等の実形状と の差、及び測定系の誤差に原因があると考えられる。

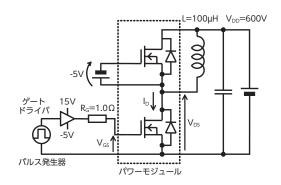

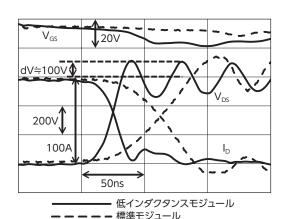

次に、低インダクタンスモジュールのスイッチング動作を評価した結果について述べる。 $\mathbf{図9}$ はそのスイッチング評価回路であり、動作条件は $V_{DD}$ =600V,  $I_{D}$ =100A,  $V_{GS}$ =-5V/15V,  $R_{G}$ =1 $\Omega$ である。また、標準モジュールを低インダクタンスモジュールと同じ過電圧dVとなるようスイッチングさせた。過電圧はゲート抵抗 $R_{G}$ を調整することで行った。低インダクタンスモジュールと標準モジュールの測定波形を $\mathbf{図10}$ に、測定波形より得られたターンオフ時間を $\mathbf{表2}$ に示す。過電圧dVは約100V、低インダクタンスモジュールのターンオフ時間tfは20nsと設計通りの結果が得られ、低インダクタンスモジュールはSiC MOSFETの高速性に十分に適応したパワーモジュールということが実動作でも検証された。

また、標準モジュールに対して約1/3のターンオフ時間が得られた。一般にパワーモジュールのターンオフ時間は過電圧が定格電圧を超えない範囲で早くなるよう設定される。このため、標準モジュールに対しターンオフ時間を1/3まで短縮することが可能であり、スイッチング損失の低減が可能である。

図9 スイッチング評価回路

図10 ターンオフスイッチング波形

表2 ターンオフ時間

|          | 単位 | 低インダクタンス<br>モジュール | 標準<br>モジュール |

|----------|----|-------------------|-------------|

| tf       | ns | 20                | 58          |

| td (off) | ns | 59                | 79          |

# 5. 結 言

SiC MOSFETの高速スイッチングに対応するため、寄生インダクタンスを低減する事でターンオフ時の過電圧を抑えた低インダクタンスモジュールを開発した。結果、標準モジュールに対して約1/3倍のターンオフ時間でのスイッチングが可能であることを示した。

####

- (1) 木村ら、SEIテクニカルレビュー第183号、pp.125 129 (2013)

- (2) 日吉ら、SEIテクニカルレビュー第183号、pp.130 134 (2013)

- (3) JEC2407:2007、絶縁形パワー半導体モジュール

- (4) K. Wada et al., ISPSD, pp.225 228 (2014)

- (5) 斎藤 ら、SEIテクニカルレビュー第186号、pp.69 74 (2015)

執 筆 者

**豊島 茂憲\*:パワーデバイス開発部**

初川 聡 : パワーデバイス開発部 主幹

平方 宣行 : エネルギーシステム機器開発部 主幹

**築野 孝** : パワーデバイス開発部 グループ長

(理学博士)

御神村泰樹 :パワーデバイス開発部 部長

\*主執筆者